4 bit full adder truth table4/5/2024

Ncsim: *W,RNQUIE: Simulation is complete. Instantiate the design and connect to testbench variables

The code shown below uses an always block which gets executed whenever any of its inputs change value. The code shown below is that of the former approach. A logic circuit used for the addition of two one bit signals.

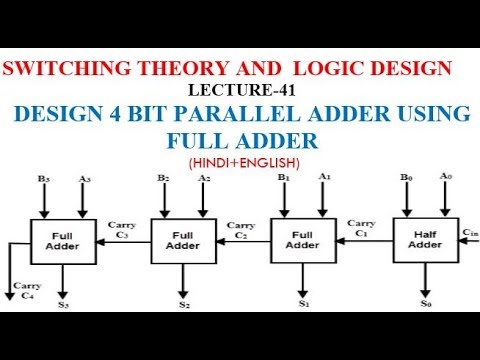

Since an adder is a combinational circuit, it can be modeled in Verilog using a continuous assignment with assign or an always block with a sensitivity list that comprises of all inputs. To set up full adder circuit using NAND gates only and to verify the truth table. Note down the output readings for half/full adder and half/full subtractor sum/difference and the carry/borrow bit for different combinations of. An example of a 4-bit adder is shown below which accepts two binary numbers through the signals a and b which are both 4-bits wide.

0 Comments

Leave a Reply.AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed